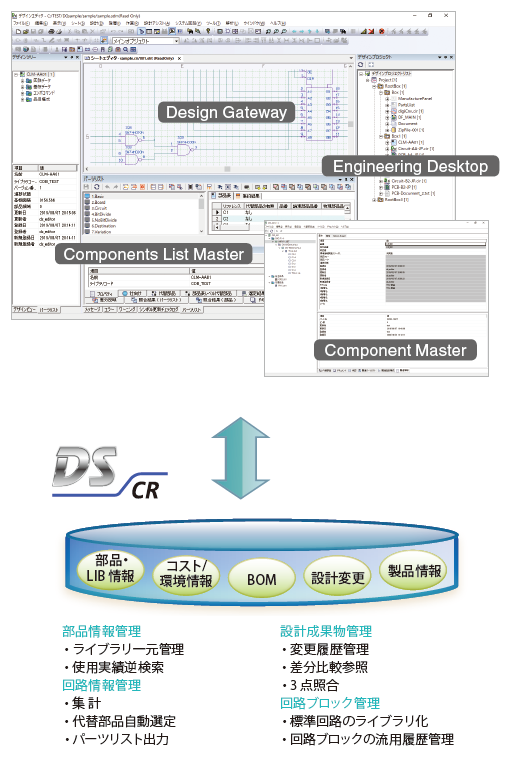

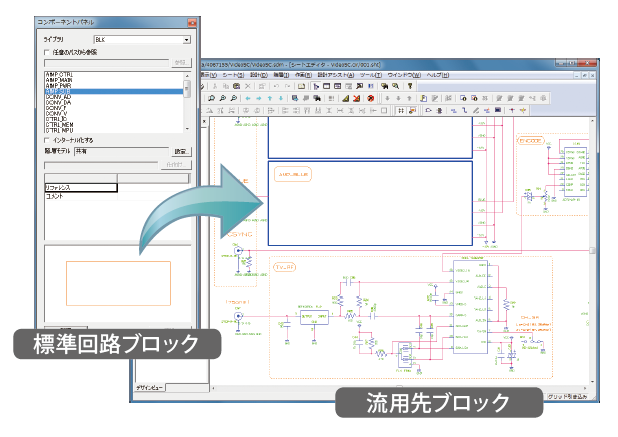

階層・回路ブロックを用いたモジュール設計

Design Gatewayでは、標準化したい機能ブロックやモジュールを標準回路ブロックとしてライブラリ化でき、標準回路ブロックは、流用先の回路において部品ライブラリのように検索・入力できます。

また、回路ブロックは流用先での様々な編集権限の設定が可能で、運用に応じた回路ブロックを利用した流用設計ができます。

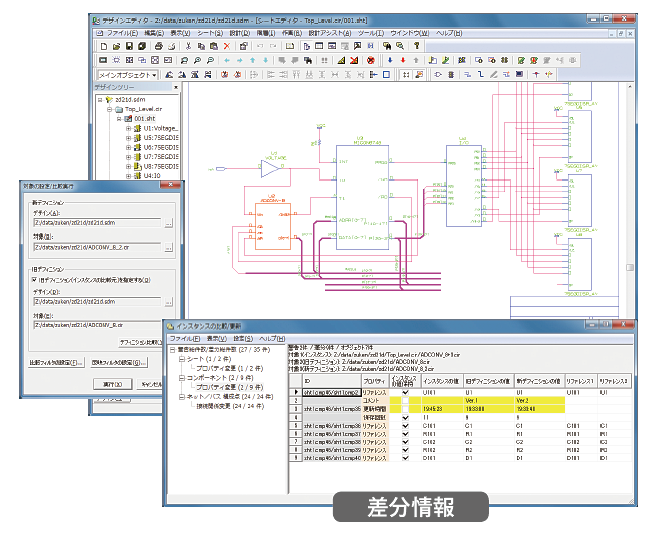

流用元回路ブロックが更新された場合、流用先回路ブロックとの差分を部品やネットなどのオブジェクト毎に抽出することができます。

また、流用元回路ブロックの情報を流用先回路ブロックに反映する際、差分毎に流用先の情報を保持させることができるため、流用先回路ブロックの編集内容を優先させたいというケースにも対応できます。