概要

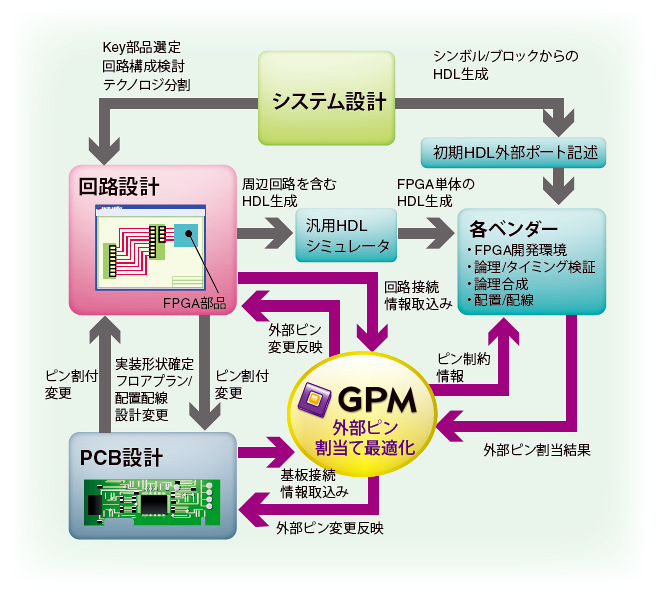

高機能、高集積、低コスト・短納期のニーズを背景に、広範な分野で FPGA 部品が採用されています。詳細回路設計において、ハイスピード対応や基板上の配線効率向上などのために、回路設計、基板設計、そして FPGA 設計の各設計プロセスでの擦り合わせが必然的に行われています。

例えば、基板レイアウト/層数の制約に従って、FPGA 部品に接続する差動信号ラインやバスラインなどをどのピンに割り当てるかの検討と反映があります。その頻度の高さと情報量は、各設計プロセスへの負荷となり、ヒューマンエラーを起こす要因にもなります。

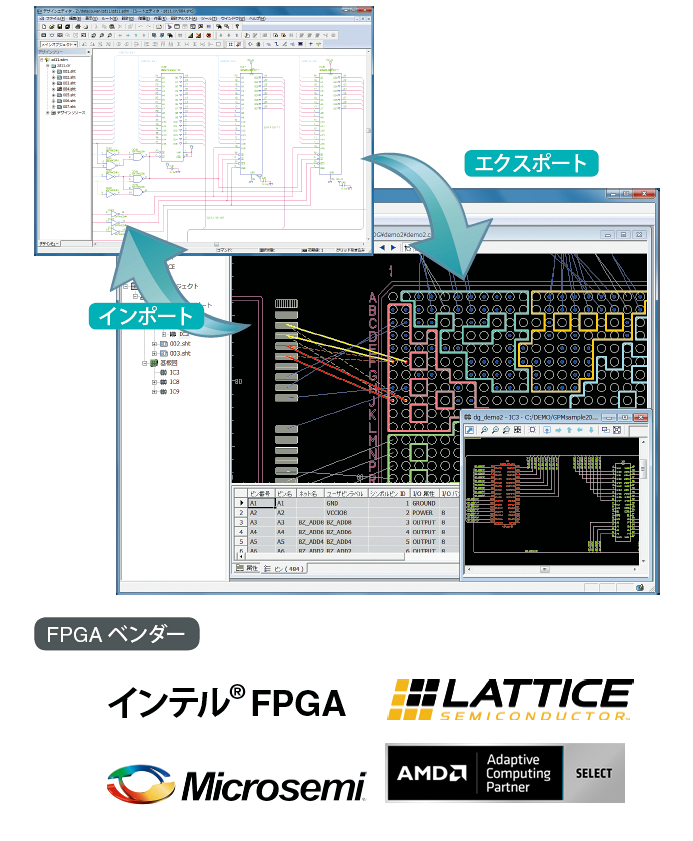

GPM は、各設計プロセスに加え、CAD ライブラリ管理を含めた連携を図ることで、FPGA 部品を取り巻く回路 / 基板設計の全体最適化を提供します。

●CAD ライブラリ、FPGA、回路、基板の4つのプロセスの連携

●FPGA 部品を取り巻く基板設計全体の最適化

●グラフィカルなビューによる情報の可視化

●直感的なツール操作環境の提供