図研は、産官学連携によって半導体業界のR&Dエコシステム創出を目指す「3Dへテロ集積アライアンス(代表 井上 史大、横浜国立大学 准教授、以下3DHI)」の活動趣旨に賛同し、同アライアンスへ参画しました。

近年、半導体デバイスの高性能化・低消費電力化を実現する技術として、チップレットなど異なる機能を持つICチップを積層する「3Dヘテロ集積」(ヘテロジニアスインテグレーション)への注目が高まっています。図研は、地元横浜市にある横浜国立大が中心となって、この技術分野での産官学連携を進める「3DHI」への参画を通じ、次世代半導体開発のイノベーション創出に貢献することを目指します。

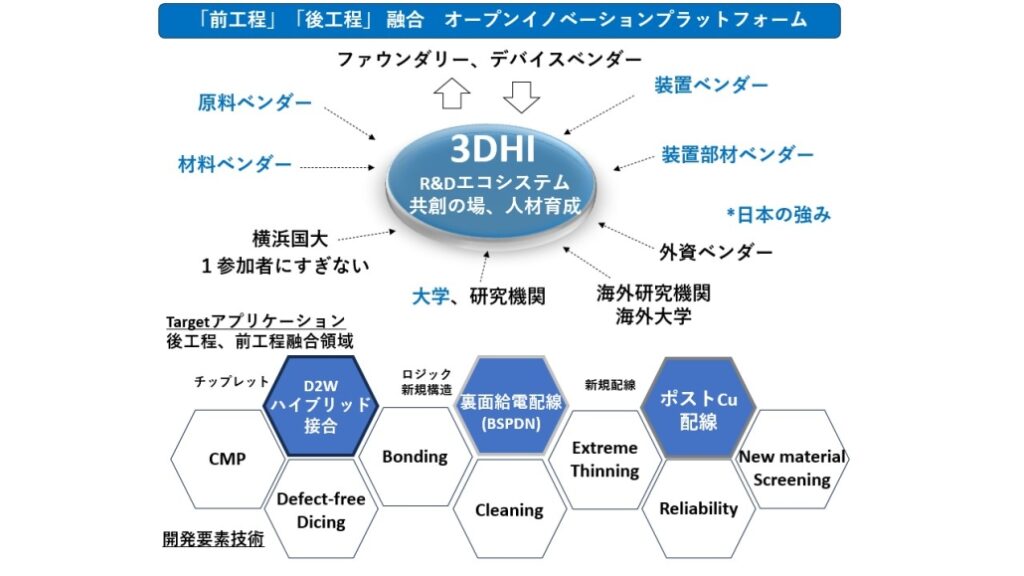

■ 3Dへテロ集積アライアンス(3DHI)について

3DHIは、「3Dヘテロ集積デバイス」の形成とそのプロセスをテーマに、産官学連携の研究開発や情報提供を行い、半導体産業に貢献することを活動目的する非営利団体です。2023年4月に横浜国立大学発のHIYA(3D半導体コンソーシアム)と大阪公立大学の3DPI(半導体3D実装材料プロセス・インフォマティクス研究会)が合併し設立されました。現在、国内外の大学、官民研究組織をはじめ、80社以上の半導体材料・装置・デバイスメーカーが参画しています。

■ 図研の「3Dヘテロ集積」に対する取組み

チップレットや3D-ICの開発は、個々のチップだけでなく、チップ間やインターポーザ、パッケージまで含めたシステムとして全体最適を考慮した設計・解析環境が求められています。図研は、主力製品であるシステムレベルマルチボード設計・検証環境「CR-8000 Design Force」が有する3D描画や自動配線機能を強化し、チップレットをはじめとした「3Dヘテロ集積」技術の設計・検証に貢献することを目指しています。また、Synopsys社やAnsys社と協調し、両社のツールとシームレスに連携する新たな3D-IC設計・解析の開発環境の提供に取り組んでいます。

【本件に関するお問い合わせ先】

株式会社図研

コーポレートマーケティング室

電話:045-942-1511(代表)

フォームでのお問い合わせは こちらから