☑Products

図研ベテランSEによる知って得する機能解説

-GPM編-

2011.04.21

前回は、ピンアサイン変更に伴う手戻りコストと、そのピンアサイン変更を手際よくCADに反映できるGraphical Pin Manager(以下、GPM)の様々な機能についてご紹介しました。(前回記事はこちら )

)

今回は、GPMの導入効果と、ピン数の多いFPGAパッケージデバイスの「CADライブラリ登録」や「回路図作成」を支援する便利機能についてご紹介したいと思います。

■GPM導入効果

まずは、GPMを活用したピンアサイン変更の費用効果について、実例ベースの近似値ですがご参考として紹介したいとおもいます。

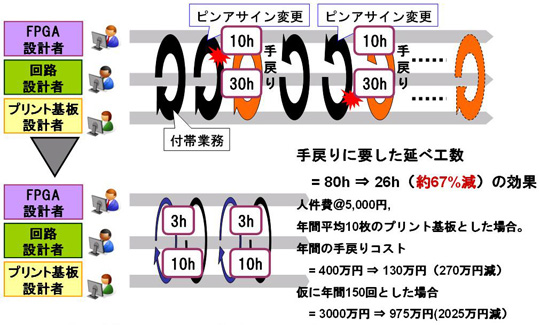

1枚のプリント基板にFPGAを実装する設計で、2回の手戻りでピンアサイン変更があった場合。人件費は¥5,000と仮定して試算。

ピン変更リストをもとに、FPGA設計側でコンストレインツ反映およびインプリメントに要していた時間。 10時間→3時間

回路図およびプリント基板への情報反映にかかっていた時間。 30時間→10時間

延べ工数 80時間→26時間。 約67%工数削減効果がありました。

前回の例を参考に、費用(*)に換算すると・・・

年間平均10枚のプリント基板の場合、コスト270万円減に。

そして、年間150回のピンアサイン変更とした場合、2025万円減の費用効果となります。

実例ベースですが、近似値としており数値及び費用は実際のものではありません。

■CADライブラリ登録支援

次に、CADライブラリ登録を支援する機能についてご紹介します。

CADで回路図を描こうとした場合、また、プリント基板図を描こうとした場合、CAD用のライブラリが必要になります。

FPGAデバイス・パッケージの多ピン化がここ数年の間に一気に進み、ハイエンドデバイスのパッケージでは2,000ピンに届きそうな勢いです。現在は500ピン~800ピンが主流のようですが、近い将来1,000ピン前後になりそうです。この規模のCADライブラリを作成する場合、少なくとも3~4日を要します。

ライブラリ登録の担当者は、データシートを取り寄せて、参照し、転記したりしながらの作成になりますので、確認作業を含めて時間がかかります。

GPMではFPGAのデバイス情報を持っており、その情報にはFPGAデバイス毎のピン情報が含まれます。GPMのライブラリ生成機能では、そのデバイス情報を利用することができますので、既存のフットプリントと紐付けてCADパートライブラリを作成することが可能です。

この機能により、ピン数が多くても、十数秒程度でCADライブラリパートを作成することができますので、CADライブラリ登録の生産性は上がります。

どのようなデバイス情報が収録されているかはこちら をご覧ください。

をご覧ください。

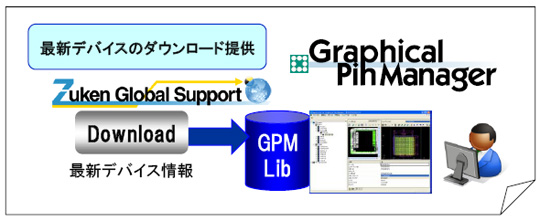

この情報は、GPMソフトウェアのインストーラーにも同梱されていますが、『Zuken Global Support』より、最新のデバイス情報をダウンロードして更新することが可能です。

前のページへ

前のページへ