☑Products

図研ベテランSEによる知って得する機能解説

-GPM編-

2011.03.24

■はじめに

FPGAのピンアサイン変更が発生し、思わぬ手戻りと工数を要したことで、苦労された設計者の方は多いのではないでしょうか?また、苦労だけでなく思わぬロスコストを発生してはいないでしょうか?

プリント基板回路設計と突き合わせて、ピンアサイン変更をする際に手際よくCADに反映できたら、という思いに駆られている方々は多いと思います。

今回は、FPGAとプリント基板回路の協調設計として提案しております「Graphical Pin Manager(以下、GPM)製品」についてご紹介させていただきますが、GPMソリューションの背景と内容について、製品カタログに書ききれなかったことを中心に触れていきたいと思います。

まさに現在お困りの方はもとより、設計現場のコスト/ロスコストを少しでも抑えたいとお考えになっている方には、ぜひお読みいただければ幸いです。

■設計現場において

FPGAを含めた回路設計の現場では、FPGA内部回路、基板回路、そしてプリント基板の設計を担う方々がいます。設計規模によっては兼務する方もいます。

(厳密には他の役割を担う方々もいますが、ここでは便宜上、三者とさせていただきます。)

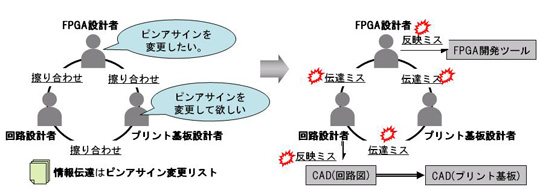

ピンアサイン変更の要求は、FPGA設計側またはプリント基板回路側のどちらからでも発生しますが、各々勝手に行えるものではなく、双方擦り合わせをします。変更ボリュームにもよりますが、その擦り合わせにはそれなりの時間を要しますし、もし双方の設計拠点が遠隔地であった場合は、必要に応じてどちらか一方が出張することになります。

その擦り合わせの中で、ピンアサイン変更内容の伝達はどのような手段で行われるのでしょうか。変更がごく小規模で双方の担当者が近くにいる場合、口頭で伝えるケースがありますが、変更一覧リストなどの資料を作成して、渡すケースが一般的でしょう。

FPGA設計側は、変更リストに基づいて、開発ツールのコンストレインツファイルに書き写していきます。

回路設計側では、同様に回路図上の信号線の引き直しを行い、プリント基板設計者に反映後のネットリストを渡します。

プリント基板設計者は、ネットリストを受取り配線パターンの設計を進めていきます。

以上が一般的な流れと言ってよいでしょう。

実は、この中に手戻りを起こしてしまう要因があります。

■手戻りを起こす要因とは

ピンアサイン変更リストを人手で作成しているので、記入ミスや記入漏れを起こしている場合があります。このまま後の工程に行った場合、FPGA側では開発ツールでDRCエラーになり、コンパイラが通らないとか、プリント基板では配線パターンが引かれていないといったトラブルを起こすことになります。

ピン変更リストが正しい場合でも、FPGA設計側でコンストレインツファイルに写し変える際の反映ミスを発生する可能性があります。

回路図に反映する際には手動による信号線の引き直し作業が発生します。その工数は変更ボリュームや回路図の描かれ方で増大していきます。その作業後にピン変更リストと突き合わせて確認作業を行います。

ここでもし反映ミスが発生すると、後工程のプリント基板設計において誤った配線パターンで設計されることになり、実装されたFPGAデバイスにプログラムデータを流し込んでも回路が動作しないというトラブルになっていきます。

そうしたミスの発見が後工程になればなるほど増大し、コストに影響してきます。手戻りのコストは設計頻度を考慮して年単位で換算すると大きなものになっていきます。

前のページへ

前のページへ