Products

図研ベテランSEによる

知って得する機能解説 -BD編-

2007.06.21

「えっ、そんなこともできるの?」

日々多機能化するEDA製品。リリースのたびに実装される新しい機能はどれも厳しい開発スケジュールに追われる図研開発陣の汗(残業?)の結晶です。そんな機能があまり有効に使われていないとしたら、これほど悲しいことはありません。そんな意外に知られていないお役立ち機能をシリーズでご紹介していきます。まず今回は…

「電位差クリアランス機能」と「電位分布図機能」です。

図研のプリント基板設計ツール、CR-5000/Board Designerでの豊富な配置機能、パターン配線機能、アートワーク機能は、おかげさまでご好評をいただき、様々な局面で効果的にご 活用いただいておりますが、 皆様に 意外に知られていない機能もあります。今回ご紹介するのもそんな機能の一つです。

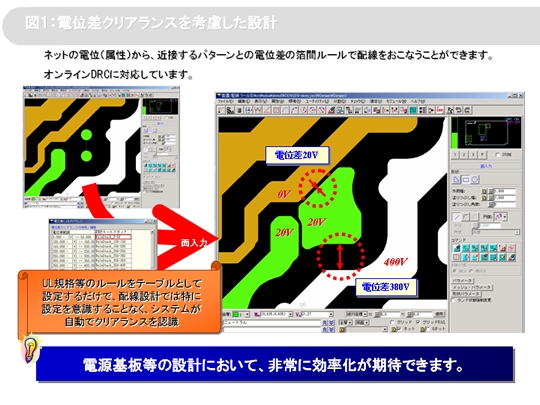

パターン配線では、信号と信号が近接する場合、電気的制約条件をもとに、箔間クリアランスを守り、配線をする必要があります。勿論、一般的な信号間の箔間クリアランスを守り、配線をする機能は、どのプリント基板ツールでも対応されています 。しかし、電源系統の信号を扱う場合、UL規格など安全規格に準拠し、交流電流の電位値(最低電位値 / 最高電位値)を考慮した箔間クリアランスルールを守った設計機能が求められます。

CR-5000/Board Designer では、Rev8.0より(現状Rev10をリリース予定)これらの 設計制約を支援する機能として、図1:に示す 「電位差クリアランス機能」を搭載しました。従来設計者は異なる信号間の電位差を計算し、UL規格などのルールテーブルから箔間クリアランスを導き出し、設計していく必要があったため 、大きな負荷になっていました。

本機能は、各信号間の電位差算出、ルールテーブルからのクリアランス値取得を自動化することで、効率的なパターン設計を実現します。

前のページへ

前のページへ