☑Club-Z特集

実装軽視に物申す!

第2回:JISSOでもう一度日本が勝つ道 キーワードは「3D」と「規格化」

福岡大学 工学部 電子情報工学科教授・工学博士

友景 肇

2011.08.25

前回は、かつて半導体産業で日本と海外で起こったことを振り返ることから、モノづくりにおける日本再生の一つのキーワードとして、部品内蔵基板を含む三次元実装設計という技術の位置づけについて説明した。(第1回記事はこちら )

)

今回は、この分野で今後日本がイニシアチブを取るべくスタートした、福岡県での取り組みについて紹介していきたい。

■福岡県の先端システムLSI開発拠点構想とSiPプロジェクト

福岡県の麻生 渡 前知事は、産業振興に熱心で、自動車や半導体の企業誘致や振興政策を積極的に行った。半導体では、シンガポールから九州までを海のベルトで結び、シリコンシーベルトと称して、ベルト地域での半導体設計・生産の拠点化とネットワーク形成を推進した。また、研究開発のための事業として、文部科学省の知的クラスター創成事業への福岡県の提案が採択され、2002年から2007年までの5年間に、毎年5億円の研究予算で5つのプロジェクトが走った。その中の1つに【SiPモジュール設計技術の開発】があった。2002年当時、システムLSIに関心が集まり、SiPは今ほど関心がない時期であった。当時を思い出すと、このプロジェクトを立ち上げるときのミーティングで、トヨタの車作りが話題となり、「車の歩留まりは100%」「新車開発には優れたCADが使われていて、パネル上のボタンを押す感覚もシミュレーションできるらしい」「半導体のモノづくりは車に比べれば大人と小学生の違いかも、もっとシミュレーション技術を上げよう」などの話が出た。大学と企業が集まった5年間のプロジェクトで、SiPを設計するための3次元EDAツールSTEERSIPを開発し、SELBICと称するフリップチップ接続を非接触で評価する装置や実装工程を評価するためのTEG( Test Element Group)チップ、TEGを実装する標準基板RSを開発した。また、2005年には、SiPを中心とした高密度基板の標準化を目指したSIPOS(System Integration Platform Organization Standards)という組織を福岡で立ち上げた。

SIPOS立ち上げは、アメリカのプリント基板協会IPCが展開していたプリント基板の世界戦略の話から始まった。IPCがPCQR2という組織を作り、プリント基板のテストクーポンを無料でプリント基板メーカに配信していた。プリント基板メーカがテストクーポンに従って作ったプリント基板をCATという会社が電気テストを行ない、認定を出す仕組みで、認定がもらえればインテルなどから基板の発注が受けられる。アジアでは、日本以外ではほぼすべてPCQR2の網にかかっていることを知り、このままだと日本のプリント基板メーカはIPCにやられてしまうとの危機感から、独自にTEGや基板を作って評価方法を共通化させ、実装工程での知見をデータベース化することを目指した。

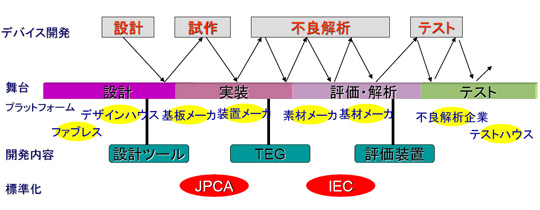

知的クラスター事業の5年間のプロジェクトが終了した2007年、福岡県は更に大きな知的クラスター事業II期を走らせることにし、20を越えるプロジェクトで、年間18億円の研究経費で5年間の文部科学省プロジェクトがスタートした。SiPプロジェクトは、【半導体実装プラットフォームの研究開発】と名前を変えた。図1は、この研究テーマを説明するためのものである。新しいデバイス開発をしたい企業が、あたかも劇場の舞台の上をピンポン玉が転がっていくように、設計、試作、不良解析、テストを素早く行うことができる場となるプラットフォームを福岡に構築しようというものである。舞台を支える柱は3本あり、[EDAツール] [実装評価装置]及び[評価用TEGチップ]である。この舞台の周りにはファブレスから始まって、基板メーカ、装置メーカなどがいてビジネス面で支援してくれる。途中、事業仕分けで名称が地域イノベーションクラスター事業と変わったが、同じ体制が続いており、今年2011年度が最終年度である。II期では、3次元SiPツールにMEMSデバイスを実装して、応力解析を行える機能を付加し、TEGでは絶縁層にlow-k材を用いた先端TEGやシリコンインターポーザなどの開発を行っている。

図1 地域イノベーションクラスター事業「半導体実装プラットフォームの研究開発

地域イノベーションクラスター事業の出口の1つとして、福岡県は半導体実装の研究機関を作ることを計画し、知事自らドイツのフラウンフォーファIZMなどを訪問した。私も、知事に同行したが、アイスランドの火山爆発で視察旅行は計画の半分が中止となった。現在、世界中で大規模な半導体の製造に関する研究が進行中であることは前回説明した。単なる評価装置が並んだ研究所や、海外を真似た研究所を作る愚はない。作ることになる研究所のコンセプトは、以下に説明する部品内蔵規格部会から生まれた。

■JPCA部品内蔵規格部会

まず、部品内蔵規格部会がJPCAに生まれた経緯を簡単に説明する。部品内蔵基板は、受動素子や能動素子を基板内部に埋め込む構造で、実装密度が上がるために携帯端末など小型で高密度なシステムに有効である。しかし、それのみでなくチップが埋め込まれているため、熱応力などを上手く制御できれば、表面実装以上に信頼性が高くなり、車載などへの応用が期待されている。部品内蔵基板をビジネス的に大きくするためには、学会という中立な立場での意見交換が大事である。エレクトロニクス実装学会(JIEP)の中に、2007年4月にEPADs(Embedded Passive and Active Devices)研究会が誕生した。これが、部品内蔵基板の設計から評価までを研究する組織となり、企業を越えて部品内蔵基板を議論する場が日本に出来た。

一方、プリント基板業界で組織されている日本電子回路工業会(JPCA)でも、部品内蔵基板技術を海外に持って行かれることを危惧し、技術の囲い込みとこの分野での世界的なイニシアチブをとることを目指して、2008年3月に部品内蔵基板規格部会を立ち上げた。まず部会で行ったことは、言語の統一であった。基板メーカごとに呼称が異なり、いわゆる方言がたくさんあったものを標準語に統一した。また、各社各様で製造方法が異なっているものを14種類に大別した。更に、SIPOS TEGを用いた試験方法を明記した。3カ月で規格書を書き上げ、2008年6月に世界初となる部品内蔵基板規格EB-01(Edition 1)を発表した。これは、すぐに英語化、中文化され、翌2009年には、基板の表裏を定義し、基板内部にあるチップの接続端子を規定する呼称を示した。基板のどちらを表としてもよいように思われるかもしれないが、基板に内蔵された部品の位置を特定するためには、どちらかの面から数えて何層目に部品があるかを決める必要があり、基準となる面がいる。表面の定義は、実装されている部品の端子数が多い面を表面と定義した。ただし、二次実装で、マザーボードに実装される場合は、その反対面を表面とした。2010年6月に発表したEdition 3では、新たなSIPOS TEGを使った試験方法を規定した。この年の12月にIECの投票でPASレベルでEB-01は国際標準となった。更に、2011年6月には信頼試験方法などを加え、設計ガイドを大幅に見直したEdition4を発表した。

プリント基板の分野の中で、部品内蔵基板には日本に優位性があり、標準化でイニシアチブが取れている数少ない領域である。また、通常の多層基板と違い、プリント基板メーカだけでは開発できない領域である。どのような材料物性の材料が必要で、どのような装置で実装すれば接続の信頼性が上がるのかなど、材料メーカや装置メーカと一緒になって開発する必要があり、しかも日本の材料メーカや装置メーカは世界でも強いという優位性がある。

前のページへ

前のページへ