☑アナログ&ミックスド・シグナル回路の設計と

基板レイアウトで知っておくべき基礎技術

13. デジタル回路の部分もなめてかかってはいけない②

アナログ・デバイセズ株式会社 石井 聡

2011.08.25

13-3 サンプリング・クロックは高いスペクトル純度が必要

■安易にクロック発振器を設計してはならない

サンプリング・クロック発振器には、高いスペクトル純度が必要です。RC弛張発振器は回路自体がコンパレータのように機能することから、振幅ノイズが位相ノイズに変化して出力に大きく現れるため、使用できません。LC発振器の位相ノイズはRC弛張発振器よりは「まし」ですが、それでも充分ではありません。

位相ノイズを最小にするには水晶発振器が最適です。きわめて高速なクロック信号の場合はSAW(Surface Acoustic Wave:表面弾性波)発振器がよいでしょう。

■インバータICを使った水晶発振器でも適切ではない

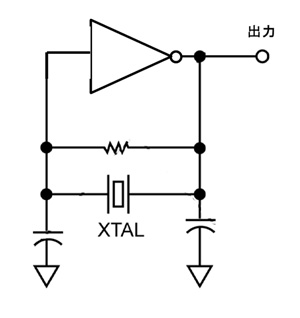

水晶発振器の設計でよく見るものは、図13-3のようなインバータICのゲートを1つ(もしくは複数)、水晶発振子を1個、抵抗を1本~2本、コンデンサを2本使用したものです。

しかし水晶発振子や発振器の特性や性能に明るい技術者は、この回路を採用しません。このタイプの回路は位相ノイズ特性が悪く、また水晶発振子を過励振してしまう傾向があるからです(水晶発振子が破壊されてしまうほどではありませんが、長期安定性が影響を受けます)。

このような発振器を使用してもよいものは、時計の発振回路(32768Hz)やCPUなどのデジタル回路のクロックなどです。特に時計の発振回路は、低電源電圧で動作するため過励振は最小限に抑えられています。また位相ノイズは、分周することで積分されるため、それほど影響を与えません。

図13-3 水晶発振器の設計でよく見るもの(サンプリング・クロックとしては不適切)

■サンプリング・クロック発振器にはできるだけディスクリートが良い

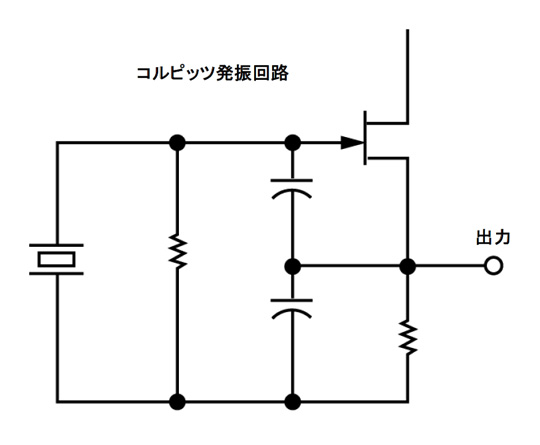

コンバータICのサンプリング・クロックに用いるものは、水晶振動子を用いる場合でも、理想的にはメーカー推奨回路で、かつバイポーラ・トランジスタやFETなどのディスクリート素子を使用してください。図13-4にこの回路例を示します。このような回路を用いることで、水晶発振子の励振レベルと、信号の位相ノイズの両方を最適化できます。

この回路の次段で信号を増幅して(たとえばここでデジタル・ゲートICを使用して)、出力信号としてコンバータICを駆動します。

図13-4 コンバータICのサンプリング・クロックとして適切なディスクリート回路構成の水晶発振回路

13-4 まとめ

示してきたように、デジタル回路においてもアナログ的な要素があります。とくにアナログ回路とデジタル回路が混在するミックスド・シグナル・システムでは、デジタル回路の視点においてもこの要素を十分に考慮することが必要です。またサンプリング・クロックは非常に取り扱いが難しい、一部アナログ的要素をもつデジタル信号です。レイアウトではとくに注意が必要といえるでしょう。

●執筆者プロフィール

石井 聡

1985年第1級無線技術士合格。1986年東京農工大学工学部電気工学科卒業、同年双葉電子工業株式会社入社。

1994年技術士(電気・電子部門)合格。2002年横浜国立大学大学院博士課程後期(電子情報工学専攻・社会人特別選抜)修了。博士(工学)

2009年アナログ・デバイセズ株式会社入社、現在コアマーケット統括部マネージャ。新規ビジネス創生、セミナ・トレーニング、技術サポートなど多岐な業務に従事。

前のページへ

前のページへ