☑アナログ&ミックスド・シグナル回路の設計と

基板レイアウトで知っておくべき基礎技術

13.デジタル回路の部分もなめてかかってはいけない②

アナログ・デバイセズ株式会社 石井 聡

2011.08.25

13-1 セットアップ/ホールド時間のタイミング変動には注意

デジタル・システム、なかでもミックスド・シグナル・システムのデジタル回路部分では、タイミング・エラーが原因で誤動作が発生しがちだといえます。これは温度変化の影響を考慮していないことがひとつの原因です。

■セットアップ/ホールド時間は常温であれば、タイミング違反になることも少ないが……

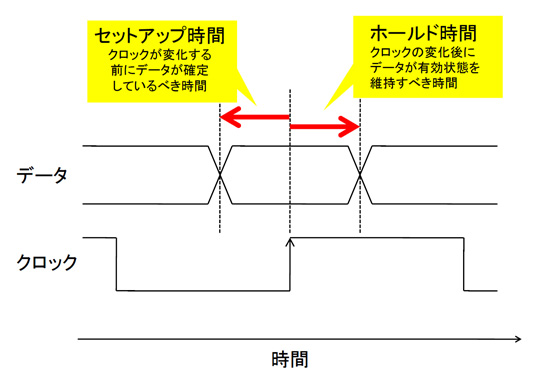

コンバータIC、メモリ、プロセッサやDSPの仕様書には、図13-1のようなセットアップ時間やホールド時間などのパラメータが記載されています。セットアップ時間はクロックが変化する前にデータが確定しているべき時間、ホールド時間はクロックの変化後にデータが有効状態を維持すべき時間です。

室温では、回路のセットアップ/ホールド時間が仕様のリミットまで到達することはあまりありません。そのため条件はそれほどシビアではないかもしれません。しかし高温や低温環境での動作状態では、回路に求められる条件は厳しくなります。

システムがデジタル回路のみで構成されている場合、入出力タイミングは温度が変化しても同じような挙動で変化する可能性が高いため、全温度範囲でシステムが機能するかもしれません(当然、確実にそうなるわけではありません)。

図13-1 セットアップ/ホールド時間の定義

■ミックスド・シグナル回路の場合はより注意して適合を確認する

デジタル・システムにコンバータICが接続されている場合、コンバータICは周辺のデジタルICとは使っているプロセス技術が異なることが多いと言えます。そのためコンバータICの入出力タイミングの変化が、周辺のデジタル回路の変化に追従せずに、タイミング違反でビットエラーが生じ、性能の低下あるいは機能しないことがおこります。

ミックスド・シグナル・システムを設計する場合は、規定の全温度範囲にわたって、回路全体でのタイミングの最大値と最小値が、仕様に適合しているかを確認しておく必要があります。少しでも疑問や心配があれば、回路構成を変更して、セットアップ/ホールド時間の仕様にすべて収まるようにする必要があります。

13-2 サンプリング・クロックはアナログでもありデジタルでもある

コンバータICに供給されるサンプリング・クロックの位相ノイズは、AD/DA変換された信号そのものの位相ノイズと見分けがつきません。そのためサンプリング・クロックに十分なスペクトル純度をもたせ、その位相ノイズを、変換する信号の最小検出レベル(1LSB)よりも小さくしておくことがきわめて重要です。

■デジタル回路部分からできるだけ分離してレイアウトする

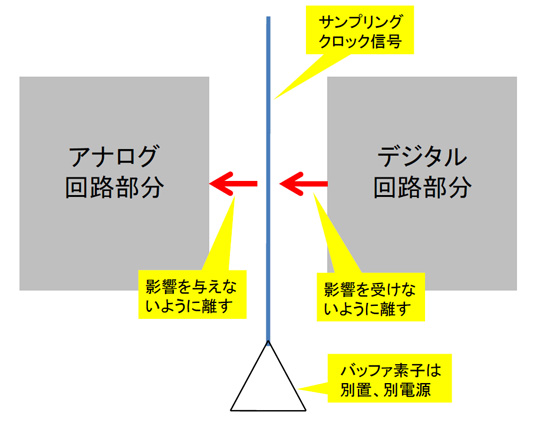

そのため図13-2のように、システムのデジタル回路部分から、サンプリング・クロック信号のパターンをできるだけ分離してレイアウトします。これはサンプリング・クロック信号がデジタル回路で発生するノイズから影響を受けないようにするためです。

サンプリング・クロック用のバッファ素子は、デジタル回路の他の部分とは、できるだけ別パッケージのICとし、このICにはノイズの少ない別電源を使用して、きちんと電源をデカップリングします。

このサンプリング・クロック信号のパターンは、システムのデジタル・ノイズが結合しないように考慮しながら、レイアウトしてください。

図13-2 サンプリング・クロック信号のパターン・レイアウトは非常に重要

■アナログ回路部分からもできるだけ分離してレイアウトする

もちろんサンプリング・クロックは「それ自体がデジタル信号」です。このためほかのデジタル信号と同様に、システムのアナログ回路部分にノイズを与えてしまう可能性があります。実際にサンプリング・クロックは、サンプル・ホールド・アンプやコンバータICに供給されるため、アナログ回路動作の性能を低下させるノイズの主原因になると考えられます。

したがってさきの図13-2のように、サンプリング・クロック信号のパターンは、システムのアナログ回路部分とデジタル回路部分の両方から分離してレイアウトしなければなりません。

つまりこのサンプリング・クロック信号のパターン・レイアウトが「きわめて厄介なもの」であることがわかります。

前のページへ

前のページへ