☑アナログ&ミックスド・シグナル回路の設計と

基板レイアウトで知っておくべき基礎技術

11.外部からの電磁干渉などから回路を守れるレイアウト

アナログ・デバイセズ株式会社 石井 聡

2011.06.16

11-1 電磁界放射による干渉

外部からの電磁界放射ノイズがプリント基板に侵入し、プリント基板上の回路動作が影響を受けることがあります。

逆に基板上の回路自体も電磁界放射を生じ、離れた位置にある別の電子機器システムにノイズとして妨害を与えることもあります。

■電磁界ノイズ放射については法などで規制されている

最近では、米国、欧州共同体(EU)や、そのほか多くの国々で、電子/電機機器から発する電磁界ノイズ干渉量や、干渉に対する回路の脆弱性(耐性)について法規制がされてきています(図11-1)。

このような法律や規制、その対応に必要とされる技術については、数多くのセミナーや書籍などがあり、またアナログ・デバイセズのアプリケーション・ノート※でも論じられています。そのためこの動向については、ここでは詳細には立ち入りません。

外部の電磁界から回路(とくにアナログ回路)を保護することは、法規制の点以外でも、現実的な問題として近年クローズアップされてきています。

図11-1 国際的なEMI放射規制の一例

※Bill Slattery, John Wynne; "Design & Layout of a Video Graphics System for Reduced EMI," AN-333, Analog Devices.

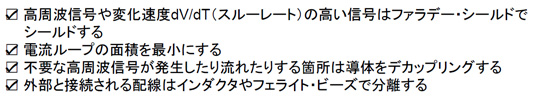

プリント基板自体から外部へ放射する電磁界放射を最小にする方法は、ここまで連載で説明してきた、図11-2のような、低ノイズを実現するためのプリント基板レイアウトの原則とも密接に関連しています。

図11-2 低ノイズを実現するためのレイアウトの原則から考える

■電磁波干渉のレベルに応じて対策が変わってくる

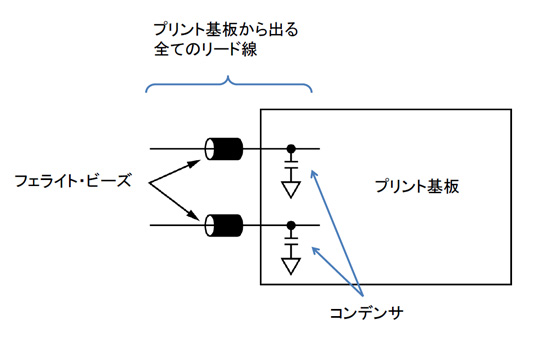

ある程度のレベルであれば、電磁波干渉(EMI)に影響されないアナログ回路を設計することはさほど難しくありません。たとえば図11-3のように、セラミック・コンデンサとフェライト・ビーズを使って、プリント基板から外部に出るすべてのリード線をデカップリングするようにプリント基板上にレイアウトすれば、かなりのレベルまで電磁波による被干渉を対策できます。

しかしながら近年では、IEC61000に代表される高度なEMIノイズ耐性を要求する規格も多くあります。これらについてはプリント基板上で十分に防護できるように、さらに注意深く設計やレイアウトを行い、厳しいこれらの試験に耐えられるだけの耐性を実現しておくことが大切です。

図11-3 プリント基板から外部に出るすべてのリード線をデカップリングする

■EMIレベルが高くなれば脆弱な回路には適切な対策が必要

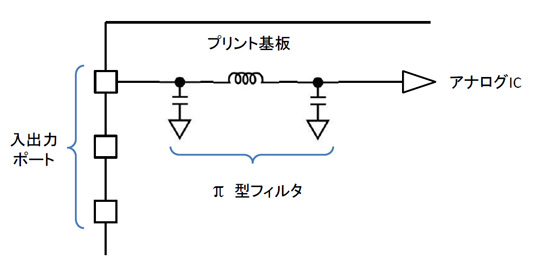

ICの入出力端子はEMIに脆弱なものがほとんどであり、図11-3で示したL型フィルタではなく、π型フィルタをレイアウトする必要が生じることがあります(前回の図10-6でも電源ノイズのフィルタとして説明した)。プリント基板上で、EMI信号が出入りする可能性がある入出力ポートは必ずフィルタ処理を行います。これはアナログ信号の入出力でも、デジタル信号の入出力でも、考え方/必要性はまったく同じです。このフィルタは「目的の信号はそのまま通し、ほかのEMI信号は通さない」ようにするためのものです。

高周波かつ高レベルのEMI環境下で動作が要求されるプリント基板では、さらにシールドで遮蔽するなどの考慮も必要です。

図11-4 より良好なEMI対策を実現するための「π型フィルタ」

前のページへ

前のページへ