☑アナログ&ミックスド・シグナル回路の設計と

基板レイアウトで知っておくべき基礎技術

4. プリント基板はあちらこちらがコンデンサ【容量】

アナログ・デバイセズ株式会社 石井 聡

2010.11.25

4-3 便利なファラデー・シールドも応用できないICのチップ内の問題

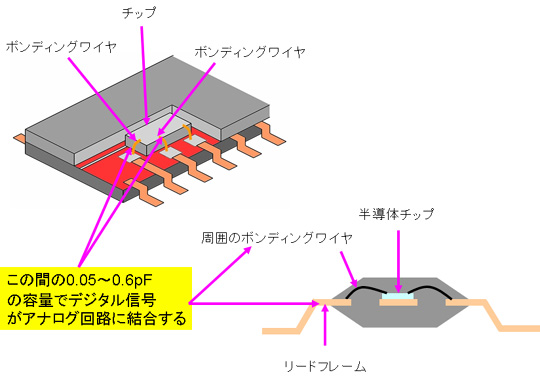

ファラデー・シールドが応用できない一例として、ICパッケージ内のボンディング・ワイヤ間があります(図4-4)。これは厄介な問題を引き起こします。

2本のボンディング・ワイヤであるとか、リードフレームとボンディング・ワイヤ間の浮遊容量は、だいたい0.05~0.6pFの範囲です。

図4-4 ICパッケージ内のボンディング・ワイヤ間で生じる容量

■ボンディング・ワイヤ間を介してノイズが伝達する

高分解能コンバータ(ADCまたはDAC)が高速なデータ・バスと接続されている場合、このデータ・バスのライン上の高速なデジタル信号は、時間変化率(dV/dt)が2~5V/nsと非常に急峻です。これによりコンバータ内部のデジタル信号ピンとアナログ信号ピンのボンディング・ワイヤ間の浮遊容量を介して、デジタル信号のノイズがコンバータのアナログ回路と結合してデジタル・ノイズがアナログ回路に伝達(発生)してしまいます。

データ・バスがスイッチするたびに、コンバータのアナログ回路部分に対して許容できないほど大きいノイズが容量的に結合し、本来のコンバータ性能が著しく低下してしまうことになります。

■基本的には打つ手は無いが、外部回路で軽減も可能

この問題に対しては現在の技術でも打つ手がありません。IC内部での対策として考えられることは、ピン間にグラウンド電位のボンディング・ワイヤを(端子として)挿入しておくくらいでしょう。

アナログ/デジタル回路がワンチップに集積されたハイスピードのミックスド・シグナルのコンバータICでは、この問題で性能が大きく制約される可能性があります。

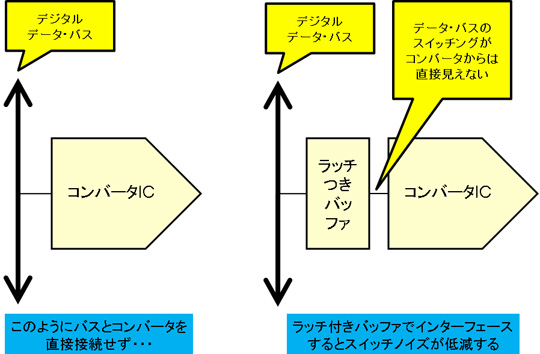

コンバータとデータ・バスを直接接続せずに、図4-5のようにラッチ付きバッファでインターフェースすることで、この問題を簡単に回避できることもあります。このバッファによりデータ・バスのスイッチングがコンバータからは直接見えないようにできるためです。

この解決方法は「コストが高くなる」「実装面積が大きくなる」「信頼性が(ごくわずかながら)低下する」「消費電力が増大する」「設計が複雑になる」といった様々なデメリットがありますが、コンバータのSN比を間違いなく改善できます。

それだけの価値があるかどうかは、個々の事例に応じて設計者が判断しなくてはなりません。

図4-5 ラッチ付きバッファをかませてコンバータとデータ・バスを接続する

4-4 まとめ

プリント基板上に形成された回路では浮遊的な容量成分がパターン間に生じます。それを適切に認知し、そして適切に処理することが大切です。とくにミックスド・シグナル回路では、デジタル信号からのノイズがアナログ信号にこの容量を通して影響を与えます。ここで示したような対策を用いて、適切に目的の機能を実現できるアナログ&ミックスド・シグナル回路のプリント基板の設計をめざしてみてください。

●執筆者プロフィール

石井 聡

1985年第1級無線技術士合格。1986年東京農工大学工学部電気工学科卒業、同年双葉電子工業株式会社入社。

1994年技術士(電気・電子部門)合格。2002年横浜国立大学大学院博士課程後期(電子情報工学専攻・社会人特別選抜)修了。博士(工学)

2009年アナログ・デバイセズ株式会社入社、現在コアマーケット統括部マネージャ。新規ビジネス創生、セミナ・トレーニング、技術サポートなど多岐な業務に従事。

前のページへ

前のページへ