☑アナログ&ミックスド・シグナル回路の設計と

基板レイアウトで知っておくべき基礎技術

4.プリント基板はあちらこちらがコンデンサ【容量】

アナログ・デバイセズ株式会社 石井 聡

2010.11.25

4-1 プリント基板上のあちらこちらで生じる浮遊容量

互いに接続されていない2つの導体間(短絡していない導体間)や、導電遮蔽板(ファラデー・シールド。以下でも説明します)で互いに完全に静電シールドされていない場合、それらの導体間には浮遊的な容量成分が生じます。

したがってどんな回路でも、実際にそれをプリント基板上に形成した場合、その基板上の回路には、多数のコンデンサ成分が内在しています。それを回路モデルに戻って考慮しないと大きな失敗をしてしまう可能性があります。

高周波性能が重要である場合、この浮遊容量の影響を考えることはきわめて重要です。DCアナログ回路や超低周波アナログ回路でさえも、動作周波数Ftの高いICが使用されることもあり、浮遊容量に起因する高周波領域の特性の不安定さに左右される場合があります。

■プリント基板上で考えるべきは「平行板コンデンサ」だけでよい

多数の電磁気学の入門書には、並列配線、同心球、同軸、その他数多くの物理的形状ごとの容量値の難しい式が示されています。

しかし我々がプリント基板上で検討しなくてはならない形状はたった1つです。それはプリント基板両面(内層も含まれます)に、導体が配置されることによって形成される、「平行板コンデンサ」です。

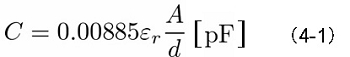

導体側面エッジの電界広がり効果を無視すれば、図4-1のような平行板において、面積をA[mm

2

]、2枚の平行板の距離をd[mm]、平行板間の絶縁物(誘電体)の比誘電率(空気を基準にした比)をεrの場合、この2枚の平行板の容量C[pF]は次式で表すことができます。

図4-1 平行板間に生じる容量を計算する

汎用のガラス・エポキシFR4基板材(εr = 4.7、d = 1.6mm)の場合、この式(4-1)から基板両面の導体間の容量を計算すると、3pF/cm

2

程度になることがわかります。

このような容量のことを、一般的に「寄生容量」と呼びます。これによって回路性能が影響を受けないようにプリント基板を設計する必要があります。

■逆手にとって活用する方法も考えられる

しかしこの基板間容量を、小容量のコンデンサの代わりとして使うこともできます。とは言っても、一般的な基板材料の誘電特性(高価なテフロン材は例外ですが)では、このようなコンデンサはかなり高い温度係数を持ち、また高い周波数ではQ値が低下してしまいます。これは現実の用途では、コンデンサとして利用できないレベルのものです。

4-2 容量間で結合する容量性ノイズとファラデー・シールド

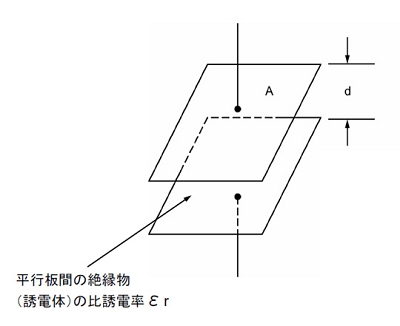

説明してきたように、絶縁物(誘電体)で分離された2導体間には、必ず容量が生じます(空気や真空も誘電体です)。このとき一方の導体の電圧が変化すると、他方の導体でも電荷の移動が生じ、電圧が発生します。図4-2にこの基本的なモデルを示します。

この図中の信号源電圧V

N

、周波数f、容量C、影響を受ける回路側のインピーダンスZ

1

のいずれかを減らせば、Z

1

に生じる電圧V

C

を減らすことはできます。しかし多くの場合、これらのひとつさえ変更できません。

図4-2 誘電体で分離された2導体間の他方の導体に電圧が生じるメカニズム

■実装が簡単でうまく働く「ファラデー・シールド」

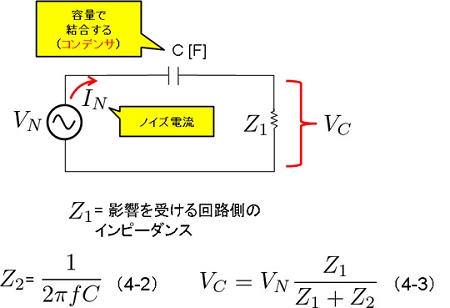

一番良い解決法は、ノイズ源とその影響を受ける回路との間に、図4-3のように接地した導体(ファラデー・シールドと呼ばれます)を挿入することです。実際は内層を1層割り当てることでしょう。

ファラデー・シールドは実装が簡単で、ほとんどの場合にうまく目的を果たします。ファラデー・シールドにより、容量結合によるノイズが生じる問題をほぼ無くすことができます。

しかしシールド効果を有効にするには、このシールドによって、ノイズ源とシールドされる(影響を受ける)回路間の電界を完全に遮断する必要があります。さらにそのノイズ源にノイズ電流を還流させなければなりません。さもないと回路のどこかにノイズ電流が流れて予想外の伝導ノイズが生じてしまいます。

また、ファラデー・シールド用の導体を未接続のままにしておくと、必ずと言ってよいほど容量が増加して問題が悪化しますので、これは絶対に避けてください。

図4-3 ファラデー・シールドのレイアウト方法と考え方

■ファラデー・シールド用の導体が未接続になってしまう例

このような問題は、半田封止型セラミックICパッケージを例として見ることができます。このパッケージでは、セラミック・パッケージ上部の金属の外枠に、正方形の導電コバール(ニッケル・コバルトの合金)の小さいふたがハンダ付けされています。

ここでパッケージ・メーカーが提供できるシールド方法の選択肢は2つしかありません。金属外枠をパッケージのコーナー・ピンの1本に接続するか、未接続のままにするかのどちらかです。

ほとんどのデジタルICでは、パッケージのいずれかの角がグラウンド・ピンなので、このふたをきちんと接地できます。

しかし多くのアナログICは、パッケージの角がグラウンド・ピンではないため、ふたはチップとは未接続のままです。この場合、全くシールドされていないプラスチック・パッケージと比較しても(同じ半導体チップが実装されていても)、電界ノイズによる影響をはるかに受けやすくなります。

前のページへ

前のページへ