複雑なIoT製品の開発リスクを、エレキ構想設計で削減!

2016年03月23日シリコンバレーにあるZuken SOZO Centerのフメアより、またまた新しい技術情報が送られてきました。IoT製品に求められる複雑な設計課題を図研のソリューションを使っていかに解決するかについて数回に分けてご紹介します。初回は、設計初期段階でエレキ構想設計を行うことの重要性についてです。IoT製品のなかでも難易度が高いウェアラブル端末を例にご説明します。

IoT社会と言われるなか、インターネットに接続されるスマート・デバイス製品(※1)も身近に感じられるようになっています。複雑な設計課題への挑戦は、もはや一部の先端企業に限られたことではなくなり、多くの企業が機能とコスト双方を両立させ競争しなければならなくなりました。

特に最近話題のスマートウォッチのようなウェアラブル業界では、一攫千金を狙って多くの企業が参入しています。参入した企業は最新のテクノロジの搭載と設計のリードタイム、性能と価格をそれぞれトレードオフしながら、ターゲット層を意識した製品を作り、ブランドイメージを構築しなければ、これからの市場で生き残ることは難しいでしょう。

スマート・デバイス(※1)

スマート・デバイス(※1)

ウェラブル端末、スマート・ホーム、スマート・カー、スマートTV、スマート・マシンなど。

ビジネス・インサイダー(米国で著名なウェブサイト)の分析によると、2017年までには全世界のインストールベースで75億個に達し、パソコン、タブレット、スマートフォンの市場を上回ると予測されています。

ウェアラブル技術は実現可能に

IoT対応製品のなかでも、ウェアラブル端末は複雑な設計課題を多く含む製品です。小型化するICパッケージに多くの機能を詰め込まなければならないのはもちろん、流線形の筐体に実装しなければならないという課題もあります。

例えばPebble Smartwatchの場合、標準的なスマートフォンの約1/5の大きさで43mm×34mm×厚さ10mmです。この中に、LEDディスプレイ、メモリボード、SoCコントローラ、センサー、Bluetoothチップ、バッテリーが、一枚の両面基板上に実装され収納されています。(「embedded」サイト参照) さらに、人間の身体・動きに合わせた筐体形状であることが求められます。

機能は増加する一方で筐体は小型化しなればならないこのようなウェアラブル端末の開発では、シグナル・インテグリティ(SI)とサーマル・マネージメントの課題解決は後回しにされてしまいます。その結果、安全規格をクリアするまでに時間がかかったり、設計への手戻りが発生したりし、市場投入までの遅延リスクを抱え込んでいます。

最新のパッケージング技術が起爆剤となる

ウェアラブル端末では複数のICをより高密度に実装する、以下のような先端パッケージング技術が求められます。

・ スマートウォッチやスマートグラスの小型で薄い筐体では、マルチチップ・モジュール(MCM)を採用。

・ システム・イン・パッケージ(SIP)の領域でも、デジタル・ロジック回路、アナログ回路、高周波(RF)回路が一つのパッケージに集積されつつある。

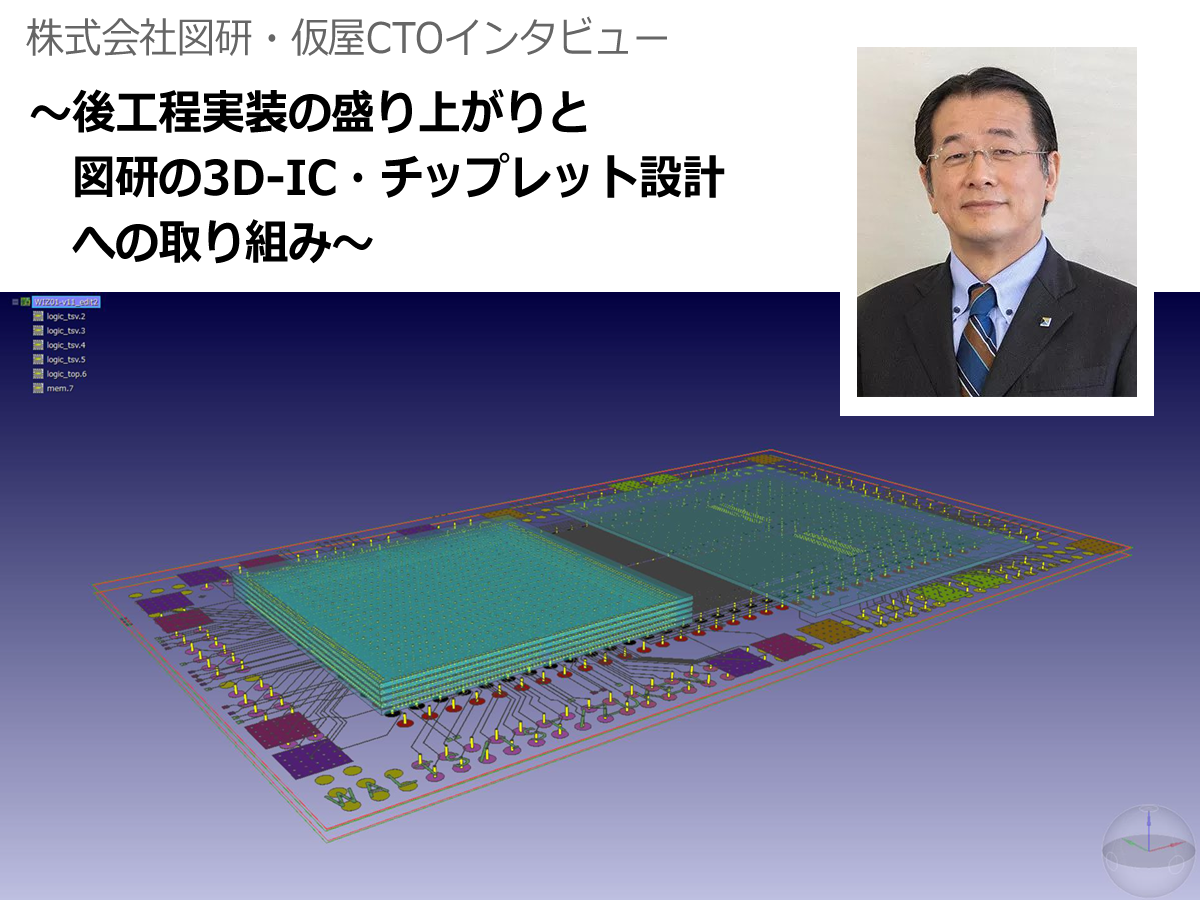

・ スルー・シリコン・ビア(TSV)を使った三次元IC実装技術が標準的に採用される。

・ パッケージ・オン・パッケージ(POP)の構造も、RAMとの配線距離を短くするために使用される。

・ PCBの実装技術でも、フレキやリジッドフレキによる高密度な基板間接続が行われ、部品も基板内や、キャビティ内、ボードを積層する際の誘電体の中への埋め込まれ始めている。

これらの技術の使用頻度が高まることで、ますます問題が複雑になっています。

設計初期段階での仕様検討の重要性

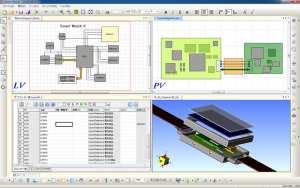

このように複雑な実装が求められる製品開発現場では、「設計プロセスの早期段階で、クリティカルな設計要件を検討すること」や「PCBと筐体を統合しながら設計すること」が重要となります。詳細な設計が決まる前に、コスト、基板枚数、重量、サイズ、筐体のフィット感などを簡単にトレードオフし評価できるバーチャル・プロトタイピングの環境構築が必要となっています。(図1)

設計初期段階で基板枚数やどの機能をどの基板上で実現させるのかが決まっていれば、それ以降に発生するリスクを大幅に減らすことができます。図研では、製品機能や部品実装レイアウト、三次元の構造の物理解析、部品表(BOM)の分析をそれぞれの1つのツールを通して、製品全体の構想設計が行えるプラットフォームCR-8000 System Plannerを用意しています。

検証事項がそれぞれダイナミックに連携することで、設計者は設計プロセスの過程で各検討要素が互いにどのような影響を及ぼすのかを把握できます。基板設計者は、筐体形状を直接レイアウトデータ内に取り込むことができるので、レイアウト設計情報が筐体設計の要求を満たしているかを確認できます。三次元筐体データと部品モデルを取り込むことで、正確な基板外形を生成できます。さらに、三次元筐体形状をフロアプラン時の制約条件として使うことができ、複数の基板間の信号インターフェースのプランニングも行えます。

いかがでしたか? 今回は、ウェアラブル端末を例に、IoT製品に求められる複雑な設計課題をいかに解決するかについてご説明しました。

次回は、リードタイム短縮に役立つ協調設計について取り上げる予定です。

ご期待ください。

【TECHNO-FRONTIER 2016で詳しい話を聞こう】

【TECHNO-FRONTIER 2016で詳しい話を聞こう】

2016年4月20日(水)~22日(金)幕張メッセで開催されるテクノフロンティアに出展します。図研ブースでは、今回取り上げたエレキ構想設計ツール「CR-8000 System Planner」のコーナーもご用意しています。ぜひ詳しい話を聞きにきてください。

詳細はコチラ

Humair Mandavia

Humair Mandavia

こんにちは。図研創造センター(Zuken SOZO Center)のエグゼクティブディレクターを務めるフメア・マンダビアです。創造センターはシリコンバレーに2013年に新しく設立されたR&D拠点です。私のキャリアは、通信業界におけるハードウェア設計者から始まり、2004年にZukenに入社し、アプリケーション・エンジニアとして働くようになりました。テキサス大学ダラス校で、電子工学の学位と経営修士(MBA)を修得しています。休日は二人の子供と自宅で過ごし、たまに友人たちとゴルフ、バスケットボール、自転車を楽しんでいます。

これからも、シリコンバレーから最新の技術情報を発信していきますので、よろしくお願いします。