☑アナログ&ミックスド・シグナル回路の設計と

基板レイアウトで知っておくべき基礎技術

12.デジタル回路の部分もなめてかかってはいけない①

アナログ・デバイセズ株式会社 石井 聡

2011.07.21

12-1 ミックスド・シグナル・システムのデジタル回路部分もおろそかにできない

連載のここまでは、ミックスド・シグナル・システムのアナログ回路部分の問題に、視点のほぼ全てをあててきました。しかし本来アナログ回路と比べれば簡単だと思われる、ミックスド・シグナル・システムのデジタル回路部分でも、基本的な決まりごとを設計者がおろそかにしてしまうことで、問題が生じることがあります。

3回に分けて、このミックスド・シグナル・システムのデジタル回路部分の問題について説明していきましょう。

■インターフェースやバス部分は問題を生じやすい

デジタル回路部分として問題が生じやすい箇所でもある、ADコンバータICやDAコンバータIC(以降「コンバータIC」と呼ぶ)のデジタルI/F部分や、(それらも接続する)プロセッサやDSPのバスでは、注意すべきポイントがあります。これらを図12-1に示します。具体的にはこの内容について、3回に分けて説明します。

一番最後については、連載のこれまで、システムの「アナログ回路部分にデジタル・ノイズが影響を与えないようにする方法」について説明してきました。しかしデジタル・ノイズ自体を、それがもともと生じるデジタル回路部分(つまり発生源)で最小限にできれば、この対策はもっと簡単なわけです。今回はとくにこのことについて説明していきます。

図12-1 ミックスド・シグナル・システムにおけるデジタル回路の要諦

12-2 まずは出力ポートのファンアウト数を考える

アナログ・デバイセズのすべてのDSP(Digital Signal Processor)と多くのコンバータICは、TTL互換のCMOS入出力ポートを持っています。入力ポートは0.8VのV

IL

(max)と2.0VのV

IH

(min)のスレッショルド、出力ポートは規定出力電流で0.4VのV

OL

(max)と2.4VのV

OH

(min)の駆動能力を持っています。DSPは容量負荷のドライブ定格も規定されており、ウエイト・ステート・クロック数を増加させずに(容量の大きい)バスにアクセスできるものもあります。

このようなDSPなどのICに接続される(負荷となる)デジタルICのファンアウト数を求めるには、デバイスのソース(吐出し)電流およびシンク(吸込み)電流、そして駆動可能な負荷容量を考慮する必要があります。それにはまず、負荷となるデジタルICのデータシートからその仕様を確認します。

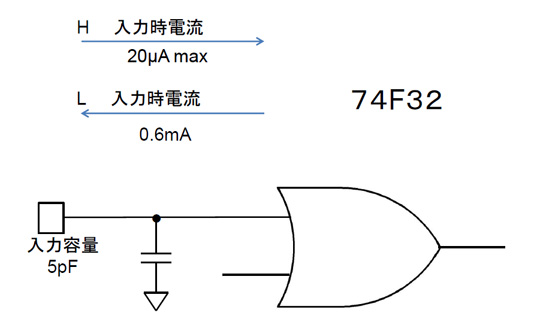

■高速TTL ICでファンアウト数を考えてみる

最近はCMOSプロセスのデジタルICがほとんどだと言えますが、基本に返って高速TTL ICについて、図12-2のように74F32(ORゲート)を負荷となるデジタルICだと考えてみましょう。74F32の入力電流ハイ・レベルの最大値(I

IH

max)は20μA、同じくロー・レベル(I

IL

max)は0.6mA、入力容量は5pF(最大)です。

アナログ・デバイセズのあるDSPを例にします。このDSPは出力がハイのときに1mAをソースし(吐出し)、出力がローのときに4mAをシンク(吸込み)できます。また最大100pFの容量を駆動できます。

これから計算すると、このDSPは74F32の20個ぶんのゲート容量を駆動でき、ハイ・レベル状態では50個分のゲート入力電流を駆動できます。しかしロー・レベルでは、わずか6.7個分(実際上は6個)のゲート入力電流しか流せません。

このうち、一番少ないゲート数が「このDSPで駆動可能なファンアウト数」になるわけです。

図12-2 高速TTL IC 74F32でファンアウト数を考えてみる

■CMOS ICでは入力容量の合計がファンアウトを決定する

このようにTTL ICが負荷となるシステムでは、ファンアウトはシンク電流によって決まるのが一般的です。

一方CMOS ICが負荷となるシステムでは、負荷のデジタルICの入力容量の合計がファンアウトを決定します。とはいえこの場合は、駆動する側のICにつながるプリント基板上のパターンやリード線の浮遊容量も考慮する必要があります。場合によってはこのような浮遊容量が制限になることもあります。常にこれらの容量の影響も、考慮する必要があります。

異なる半導体プロセスを用いた複数のICが組み合わさり、負荷回路を構成する場合もあるかもしれません。駆動側のICはこの負荷をきちんと駆動しなくてはなりませんし、ファンアウトの計算も複雑になります。しかし基本的な考え方は同じなのです。

前のページへ

前のページへ