Products

ココが凄い!Design Force 2013

-第1回:進化したハイスピード設計-

2013.08.29

スマートフォン、タブレットに象徴される高性能な小型電子機器においてはもちろん、様々な電子機器においてクロック周波数の高速化、三次元実装、半導体デバイスの多ピン化/小型化に伴うCSP化と狭ピッチ化などパッケージやボード上の伝送線路を設計する難易度はますます高くなっています。

Design Force 2013では、高速回路設計に求められる様々な機能や環境を用意しており、ビルドインされた伝送線路シミュレータ、様々なアルゴリズムを戦略的に組み合わせられる自動配線、FPGAとの協調設計環境、パッケージとボードの階層をまたがったマルチボード設計環境などの洗練された機能を駆使しながら快適に設計できます。また、FPGAベンダーや半導体ベンダー、あるいはCAEベンダー各社とのアライアンスも強化し、設計者の皆様が最新デバイスを使いやすい環境もバックアップできる環境も充実しつつあります。

今回は、これらの新機能の中から高速回路のパターンを設計する上で従来にないユニークな機能を3点選んでご紹介します。

1.信号遅延の原因となる誘電率差の発生を軽減する:ジグザグ配線機能

任意角度で折れ曲がる配線機能(ジグザグ配線機能)

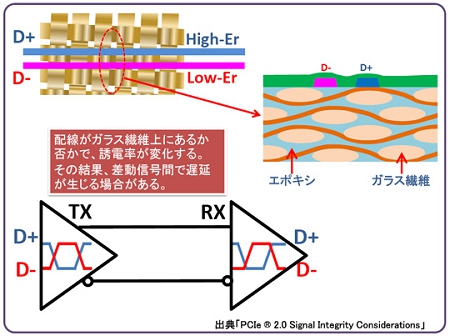

差動信号の配線方向が、基板のガラス繊維に対して垂直、もしくは水平であった場合に、ガラス繊維と配線の位置関係によっては誘電率の差による遅延が生じ、正常に機能しない場合があります。

この現象を回避するために、半導体ベンダーやFPGAベンダーが提供するリファレンスガイドでは、高速差動信号の配線に角度を付けて、配線に対するガラス繊維からの影響が均一となるように、ジグザグに配線する方法を推奨しています。

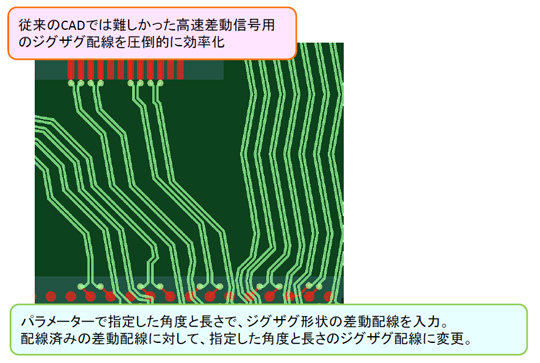

従来のCADでは困難であった配線の形状ですが、ジグザグ配線コマンドの開発により、容易にジグザグ形状で配線することが可能になり、差動信号の遅延問題の解消が期待できます。

Point!

- タイトな条件の差動信号間の遅延が軽減

- 簡単な操作でジグザグな配線形状の作成が可能

前のページへ

前のページへ